|

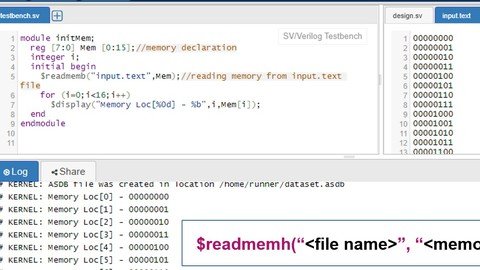

Free Download Writing Testbenches: Functional Verification of HDL Models by Janick Bergeron English | PDF | 2003 | 507 Pages | ISBN : 1402074018 | 35.2 MB mental improvements during the same period. What is clearly needed in verification techniques and technology is the equivalent of a synthesis productivity breakthrough. In the second edition of Writing Testbenches, Bergeron raises the verification level of abstraction by introducing coverage-driven constrained-random transaction-level self-checking testbenches all made possible through the introduction of hardware verification languages (HVLs), such as e from Verisity and OpenVera from Synopsys. The state-of-art methodologies described in Writing Test benches will contribute greatly to the much-needed equivalent of a synthesis breakthrough in verification productivity. I not only highly recommend this book, but also I think it should be required reading by anyone involved in design and verification of today's ASIC, SoCs and systems. Harry Foster Chief Architect Verplex Systems, Inc. xviii Writing Testbenches: Functional Verification of HDL Models PREFACE If you survey hardware design groups, you will learn that between 60% and 80% of their effort is now dedicated to verification.  Aldec Active-HDL 13.0.375.8320 | 577.5 mb Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification for FPGA and ASIC designs, advances VHDL's verification capabilities with Active-HDL, version 13.0. This latest release introduces support for VHDL-2019 protected types with generics, composites of protected types, pointers to objects of protected types and composition with protected types.  MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz Language: English | Size: 2.82 GB | Duration: 6h 47m Fundamentals, levels of design description, Datatypes, test benchs, Tasks & system tasks, FSM with examples & Projects

Mentor Graphics HDL Designer Series (HDS) 2021.1 | 743.9 mb Product:Mentor Graphics HDL Designer Series (HDS) Version:2021.1 build 1 Supported Architectures:x64 Website Home Page : Languages Supported:english System Requirements:PC * Size:743.9 mb The software developer Mentor Graphics, is pleased to announce the availability of HDL Designer Series (HDS) 2021.1 is a powerful HDL-based environment used by individual engineers and engineering teams worldwide to analyze, create and manage complex FPGA and ASIC designs.  Mentor Graphics HDL Designer Series (HDS) 2019.4 | 809.3 mb Product:Mentor Graphics HDL Designer Series (HDS) Version:2019.4 build 4 Supported Architectures:x64 Website Home Page : Languages Supported:english System Requirements:PC * Size:809.3 mb The software developer Mentor Graphics, is pleased to announce the availability of HDL Designer Series (HDS) 2019.4 is a powerful HDL-based environment used by individual engineers and engineering teams worldwide to analyze, create and manage complex FPGA and ASIC designs.  Genre: eLearning | MP4 | Video: h264, 1280x720 | Audio: AAC, 48.0 KHz Language: English | Size: 3.36 GB | Duration: 5h 2m Build a strong Verilog language foundation by implementing combinational / sequential digital circuits and testbenches  Created by Sujithkumar MA | Published 4/2021 Duration: 4h58m | 14 sections | 37 lectures | Video: 1280x720, 44 KHz | 1.7 GB Genre: eLearning | Language: English + Sub  Aldec Active-HDL 12.0.118.7745 | 550.4 mb Aldec, Inc., a pioneer in mixed HDL language simulation and hardware-assisted verification for FPGA and ASIC designs, has enhanced Active-HDL to support new features within VHDL-2019 (IEEE 1076-2019). These features simplify the language, lift certain restrictions that were present in earlier versions and introduce new application programming interfaces (APIs).  Verilog HDL: a guide to digital design and synthesis By Samir Palnitkar 2003 | 261 Pages | ISBN: 0130449113 | PDF | 8 MB Verilog HDL is a language for digital design, just as C is a language for programming. This complete Verilog HDL reference progresses from the basic Verilog concepts to the most advanced concepts in digital design. Palnitkar covers the gamut of Verilog HDL fundamentals, such as gate, RTL, and behavioral modeling, all the way to advanced concepts, such as timing simulation, switch level modeling, PLI, and logic synthesis. Verilog HDL is a hardware description language (with a user community of more than 50,000 active designers) used to design and document electronic systems. This completely updated reference progresses from basic to advanced concepts in digital design, including timing simulation, switch level modeling, PLI, and logic synthesis.  MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch Genre: eLearning | Language: English + .srt | Duration: 34 lectures (3h 58m) | Size: 1.15 GB design & verification with examples & applications |